# Hierarchical Control of Discrete Event Systems with Inputs and Outputs

Als Dissertation genehmigt von der Technischen Fakultät der Universität Erlangen-Nürnberg

Tag der Einreichung: 03. 07. 2009 Tag der Promotion: 05. 02. 2010

Dekan: Prof. Dr.-Ing. Reinhard German

Berichterstatter: Prof. Dr.-Ing. Th. Moor

Prof. Dr.-Ing. J. Raisch

### Vorwort

Mein erster Dank gebührt dem Betreuer meiner Promotion Herrn Prof. Dr.-Ing. Thomas Moor. Seine Ideen zu den wesentlichen Aspekten des Promotionthemas und die engagierte Betreuung der Promotion von Beginn an legten ein festes Fundament für meine Arbeit. Viel zusätzlicher Freiraum und das somit entgegengebrachte Vertrauen schufen ein optimales Umfeld, um auf dieses Fundament aufzubauen.

Herrn Prof. Dr.-Ing Jörg Raisch danke ich herzlich für die Übernahme des Korreferates und, zusammen mit den Herren Prof. Dr.-Ing. Bernhard Schmauß und Prof. Dr. Volker Strehl, für die bereitwillige Mitwirkung im Prüfungskollegium.

Ich danke außerdem Herrn Prof. Dr.-Ing. Günter Roppenecker, Vorstand des Lehrstuhls für Regelungstechnik der Universität Erlangen-Nürnberg. Sein beständiges Interesse an meiner Arbeit und der regelmäßige Zuspruch gaben mir das Selbstvertrauen, das für eine Promotion die notwendige Vorraussetzung ist.

Allen Kollegen des Lehrstuhls möchte ich danken, denn auf ihren Rat wie auch Aufmunterung konnte ich mich stets verlassen.

Ein ganz besonderer Dank gilt meinem Kollegen und Freund Dr.-Ing. Klaus Schmidt für die nie versiegende Quelle an fachlichen Informationen und Ideen, den Rat in allen Lebenslagen und allem voran für die Freundschaft.

Ich danke meiner Familie für den Rückhalt und für die Liebe und Unterstützung, die ich in sich wunderbar ergänzenden Facetten erfahren durfte.

Der wichtigste Dank gilt von Herzen meiner Frau Claudia, denn ihre beständige Liebe, Unterstützung und Aufmunterung waren eine wesentliche Vorraussetzung, dass diese Arbeit zum erfolgreichen Abschluss kam.

Nürnberg, Februar 2010

Sebastian Perk

### **Abstract**

In the late 1980's, the Supervisory Control Theory (SCT) was proposed by P.J. Ramadge and W.M. Wonham [RW87b], that provides a systematic method for automated synthesis of discrete event controllers with guaranteed safety and liveness properties, but fails for systems of praxis-relevant size due to extensive computational complexity. Since then, research has been aimed at design methods that are based on the SCT, but scale better with the system size by structural exploitation of the problem and thus introduce access to practical applications.

In this thesis, we propose an I/O-based framework for the design of hierarchical controllers for discrete event systems that addresses both safety and liveness properties. Technically, we build on J.C. Willems' behavioural systems theory [Wil91], that describes fundamental properties of dynamic systems like the characteristics of inputs and outputs based on their behaviours. The generality of the behavioural approach allows us to transfer this notion of inputs and outputs to discrete event systems. As a consequence, results from previous work on abstraction-based control of hybrid systems in [MR99, MRD03] could be elaborated for discrete-event dynamics.

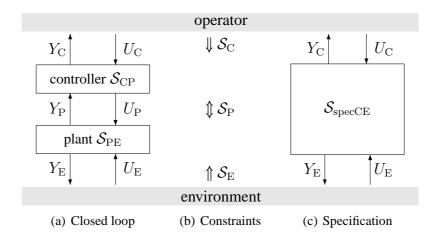

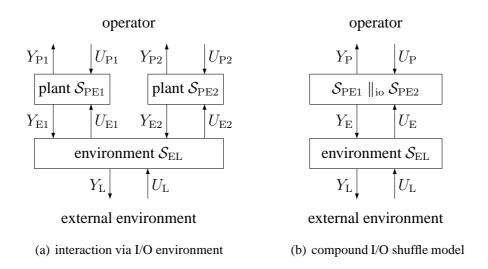

The I/O-based approach is applied to systems that consist of a number of interacting components (local subsystems) and builds a hierarchy of superposed controllers and subordinate environment models on the component models. The I/O-based description of the component models is independent of their surroundings (i.e. neighbour components or controller) to obtain reusability within different configurations. Each model of the local subsystems provides two I/O ports, one to interact with a controller and the other one to interact with the environment of the component. At first, local controllers are designed for each component according to local specifications that are independent from the component's environment. While the design method is based on the Supervisory Control Theory, safety and liveness of the closed loop are a consequence of the I/O properties of component model and controller.

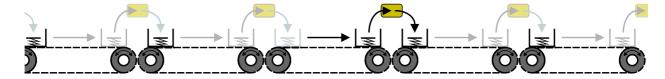

On the next layer of the hierarchy, groups of several components each are formed, and their interaction is described by a dynamic environment model. The synthesis of a superposed controller for each group is not performed on the detailed description of the locally controlled component models, but on their abstractions in form of the local specifications, which effectively limits the computational complexity. The abstraction-based controllers are proven to correctly control also the original system. By alternation of the abstraction step, the grouping of components via en-

vironment models and the design of superposed controllers, an overall system is developed that scales well with the number of system components. The expected reduction of complexity became evident also by application to the conceptional example of a transport-unit chain that comes along with this thesis.

## Zusammenfassung

## Hierarchische Steuerung von ereignisdiskreten Systemen mit Ein- und Ausgängen

In den späten 1980'er Jahren wurde mit der Supervisory Control Theory (SCT) nach P.J. Ramadge und W.M. Wonham [RW87b] ein systematisches Verfahren bereitgestellt, welches die automatische Synthese sicherer und lebendiger Steuerungen für ereignisdiskrete Systeme ermöglicht, sich aber aufgrund des erheblichen Rechenaufwands nicht für Systeme praxisrelevanter Größe eignet. Seither wird nach Entwurfsverfahren geforscht, die auf der SCT aufbauen, jedoch durch Nutzung der Prozessstruktur besser mit der Systemgröße skalieren und somit den Zugang zur praktischen Anwendung ermöglichen, siehe [PMS07b] für einen deutschsprachigen Überblick.

In dieser Arbeit wird ein Ein-Ausgangs-(E/A-) basierter Ansatz zum Entwurf hierarchischer Steuerungen für ereignisdiskrete Systeme vorgestellt, der sowohl Sicherheits- als auch Lebendigkeitseigenschaften berücksichtigt. Dieser ist angelehnt an die so genannte Behavioural Systems Theory nach J.C. Willems [Wil91], welche grundlegende Eigenschaften dynamischer Systeme, wie die Charakteristik von Ein- und Ausgängen, verhaltensorientiert und so allgemeingültig beschreibt, dass sie auch zur E/A-basierten Beschreibung von ereignisdiskreten Systemen herangezogen werden konnte. Auf dieser Grundlage lassen sich Ergebnisse zum abstraktionsbasierten Reglerentwurf für hybride Systeme aus [MR99, MRD03] auf ereignisdiskrete Systeme übertragen.

Beim E/A-basierten Ansatz wird auf einen aus Komponenten bestehenden Prozess eine Hierarchie überlagerter Steuerungen und unterlagerter Umgebungsmodelle aufgebaut. Die E/A-basierte Modellierung der einzelnen Prozesskomponenten erfolgt zunächst umgebungsunabhängig (d.h. unabhängig von Nachbarkomponenten oder der Steuerung). Dies bewirkt ihre Wiederverwendbarkeit innerhalb unterschiedlicher Anordnungen. Jedes E/A-basierte Modell der lokalen Teilsysteme verfügt über zwei E/A-Ports, einer zum Anschluss einer Steuerung, der andere zum Anschluss eines dynamischen Umgebungsmodells, welches jeweils die Interaktion einer Gruppe von Teilsystemen untereinander und mit der restlichen Umgebung beschreibt. Gemäß lokaler von der Umgebung unabhängiger Spezifikationen werden für die einzelnen Prozesskomponenten zunächst lokale Steuerungen entworfen. Die Entwurfsmethodik baut dabei auf die Supervisory Control Theory auf. Der

Nachweis von Sicherheit und Lebendigkeit des geschlossenen Regelkreises gelingt infolge der ein-/ausgangsbasierten Systembeschreibung.

Auf der nächsthöheren Stufe der Hierarchie werden jeweils mehrere Prozesskomponenten zusammengefasst und ihre Interaktion durch ein dynamisches Umgebungsmodell modelliert. Der Entwurf überlagerter Steuerungen für Gruppen von Komponenten greift nicht auf die detaillierte Beschreibung der lokal gesteuerten Prozessmodelle, sondern auf eine Abstraktion derselben auf Grundlage der lokalen Spezifikationen zurück, was den Rechenaufwand wirkungsvoll begrenzt. Die anhand der Abstraktion entworfene Steuerung steuert auch das tatsächliche System nachweislich korrekt. Durch gezieltes Abwechseln der Abstraktionsschritte, der Beschreibung der Interaktion durch Umgebungsmodelle und der Überlagerung von Steuerungen lässt sich ein Gesamtsystem entwickeln, welches mit der Anzahl der Prozesskomponenten gut skaliert. Der erwartete geringe Rechenaufwand ergab sich auch bei der Anwendung auf das konzeptionelle Beispiel einer Kette von Transporteinheiten, welches diese Arbeit begleitet.

... after all, salesmen continue to travel...

W.M. Wonham

# **Table of Contents**

| 1                                                | Intr | troduction                                                              |    |  |  |  |  |

|--------------------------------------------------|------|-------------------------------------------------------------------------|----|--|--|--|--|

| 2                                                | For  | ormal Languages: Notation and Terminology                               |    |  |  |  |  |

| 3 Discrete Event Systems with Inputs and Outputs |      |                                                                         |    |  |  |  |  |

|                                                  | 3.1  | System Description                                                      | 21 |  |  |  |  |

|                                                  | 3.2  | I/O Ports                                                               | 22 |  |  |  |  |

|                                                  | 3.3  | I/O Plant                                                               | 25 |  |  |  |  |

|                                                  | 3.4  | Constraints                                                             | 29 |  |  |  |  |

|                                                  | 3.5  | Liveness                                                                | 30 |  |  |  |  |

|                                                  | 3.6  | I/O Controller                                                          | 35 |  |  |  |  |

| 4                                                | Con  | troller Synthesis                                                       | 45 |  |  |  |  |

|                                                  | 4.1  | $Y_{\rm C}$ -Acyclic Sublanguage                                        | 45 |  |  |  |  |

|                                                  | 4.2  | Supremal $Y_{\mathbb{C}}$ -Acyclic Sublanguage: Graph-Based Computation | 51 |  |  |  |  |

|                                                  | 4.3  | Complete, Controllable and Normal Sublanguage                           | 56 |  |  |  |  |

|                                                  | 4.4  | I/O Controller Synthesis Procedure                                      | 59 |  |  |  |  |

| 5                                                | Hier | rarchical Control System                                                | 69 |  |  |  |  |

|                                                  | 5.1  | Control of Composed Systems                                             | 70 |  |  |  |  |

|                                                  |      | 5.1.1 I/O Shuffle                                                       | 71 |  |  |  |  |

|                                                  |      | 5.1.2 I/O Environment                                                   | 74 |  |  |  |  |

|    | 5.2      | Stepwise Hierarchical System Design              | 78 |  |

|----|----------|--------------------------------------------------|----|--|

|    | 5.3      | Complexity of the Transport Unit Example         | 79 |  |

| 6  | Con      | clusions                                         | 81 |  |

| Ap | pend     | ix                                               | 83 |  |

| A  | A Proofs |                                                  |    |  |

|    | A.1      | Languages and According Properties               | 83 |  |

|    | A.2      | Input/Output-Based Results                       | 85 |  |

|    | A.3      | Chain of Transport Units: Monolithic Plant Model | 97 |  |

# Chapter 1

## Introduction

When facing a complicated technical problem, a powerful instrument of successful engineering practice is to exploit the structure of the problem until it can be cast to one or a number of simpler problems whose solution applicably exists. The *control of discrete event systems* (DES) is a complicated problem. Though it has been formally solved in the late 1980's by the supervisory control theory (SCT) of Ramadge and Wonham, which delivers controllers with guaranteed correctness and performance, the model-based approach did get only limited access to industrial deployment, which is mainly due to the affinity of DES to intractable complexity of the plant model.

In contrast, engineers manage to automatize even large-scale DES such as logistics, communication networks and manufacturing systems. By practical experience and technologies like divide and conquer strategies, measurement aggregation and last but not least the hiding of apparently less relevant plant behaviour, the original problem is turned into one with manageable complexity. However, this inevitably limited view on the original problem has a number of unpleasant consequences. As correctness of the controller software cannot be formally guaranteed, usually a large number of trial and error runs is necessary for debugging. Depending on the existence and accuracy of a simulation model, a considerable number of trials run after sales on the real plant involving safety problems and high costs. Further issues are suboptimal capacity utilization as well as low configurability and low scalability. Hence the question arises how to avoid such shortcomings when organizing the problem in an applicable manner.

Since the proposal of the SCT, considerable research effort was spent on incorporating the mentioned engineering skills in model-based discrete event controller design to reduce computational complexity without the loss of the guarantees gained by the SCT. Let us introduce an example to illustrate some of the challenges in control of DES.

#### Example 1.1

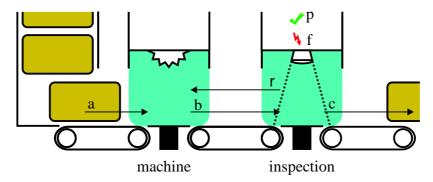

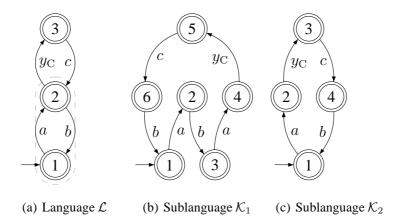

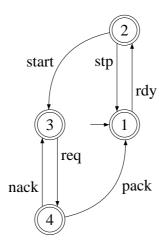

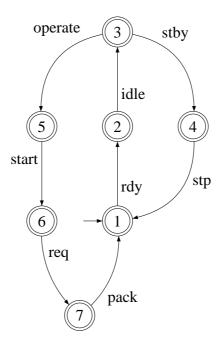

We consider a small manufacturing line as in Figure 1.1.

Figure 1.1: Manufacturing line

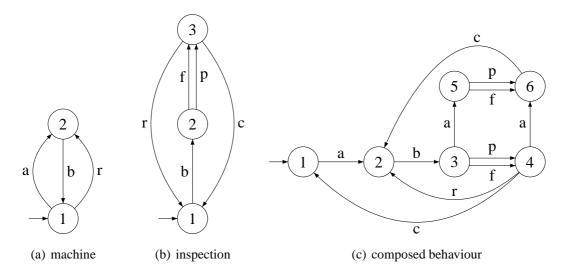

From an always filled stack feeder, raw workpieces enter a machine via a conveyor belt and are processed (a). When the process in the machine is finished, the workpiece proceeds to an inspection unit (b). The inspection results are "pass" (p) or "fail" (f). After inspection, workpieces can exit the manufacturing line (c) or return to the machine (r). The discrete event behaviour of this technical process can be represented by an automaton model of the machine and of the inspection unit, see Figure 1.2 a) and b), respectively. The occurrence of events is denoted by transitions, which are visualized as arrows labeled with the triggering event that lead from the system state (drawn as circle) before the transition to the state after the transition. The initial system state (here: states with label 1) is denoted by a sourceless arrow. The behaviour of the whole line is given by the synchronous composition of both automata, see Figure 1.2 c). The composition of all plant components is denoted *monolithic plant model*.

Figure 1.2: Manufacturing line: automata models

As can be seen, the number of states of the monolithic model is the product (rather than the sum) of the state counts of the machine and the inspection model; i.e. we face the general case, where

the complexity of the whole plant (counted in number of states) is exponential in the number of plant components.

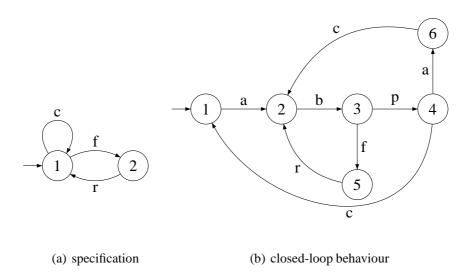

The control objective for this example shall be the reprocessing (r) of a workpiece in case it fails inspection (f). The according specification forbids the release (c) of those workpieces from the manufacturing line that failed inspection but requires reprocessing instead; it is easily formulated as an automaton, see Figure 1.3 a). For the enforcement of the specification on the plant, the uncontrollability of the events f and p has to be taken into account, as they cannot be directly disabled by a controller.

If this specification is applied directly to the plant, then the resulting behaviour blocks: consider state 6 in Figure 1.2 c) and assume it was reached from state 5 via the event f, i.e. a workpiece just failed inspection. Then, the specification forbids event c, but at the same time the required reprocessing (r) is not possible, as the machine is occupied by another workpiece. Hence, no further event is possible, and the system gets stuck in a deadlock.

The *supervisory control theory* (SCT, [RW87b]) provides an efficient algorithm to compute a minimally restrictive supervisor such that the closed-loop behaviour of the plant under supervisory control meets the given specification (*safety*) and is nonblocking (*liveness*). The resulting closed-loop behaviour of the manufacturing line is shown in Figure 1.3 b). As can be seen, the supervisor avoids the aforementioned deadlock by allowing for only one workpiece in the line until the inspection result is positive: a second occurrence of the the event a is disabled until the occurrence of the event a.

Figure 1.3: Manufacturing line: supervisory control

Note that the closed loop-behaviour can indeed be achieved by a supervisor, as only controllable events are be disabled. This fundamental condition for successful controller design is denoted

<sup>&</sup>lt;sup>1</sup>The avoidance of blockings is achieved by the marking technology which, for simplicity, is not considered here.

*controllability*. The model of the closed-loop behaviour serves as realization of the supervisor and can be implemented e.g. in the form of PLC code.

As the most appealing feature of a supervisor designed according to the SCT and as a consequence of the model-based approach, the closed-loop behaviour is *guaranteed* to comply with the specification, to be nonblocking and to be minimally restricted. On the downside of the SCT, the supervisor has to be computed on the basis of the monolithic plant model, whose complexity is prohibitive in most practical applications. Example calculation: the monolithic model of a plant consisting of 10 components with 10 states each can embrace up to  $10^{10}$  states.

The reason why, aside from the shortcomings mentioned at the outset, engineers successfully design controller software for e.g. large scale automation systems lies in the structural exploitation of the design problem: usually, the software is modular, composed of subroutines for different control tasks and different functional system components. For superposed control tasks, the view on the system is aggregated adequately by respecting only the features relevant to the task.

Since the supervisory control theory was proposed in the late 1980's, a major contingent of research in the field of discrete event systems has aimed at *structured approaches* based on the SCT that reduce the complexity of controller design and at the same time preserve properties such as guaranteed enforcement of the specification and nonblocking.

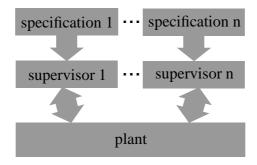

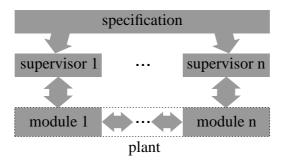

*Modular approaches* such as [RW87a, WR88, RW89, dQC00, QC00, GM04, MF08] are useful if the overall control objective is given as a set of specifications for individual tasks. One supervisor controlling the whole plant is designed for each specification, see Figure 1.4.

Figure 1.4: modular control architecture

While still the composed plant has to be computed, complexity reduction results from the low complexity of the individual specifications compared to their composition. The possibility of conflicts (in case the interaction of the modular supervisors causes blocking) requires the test for nonblocking closed-loop behaviour e.g. as in [FM06] or structural conditions that avoid conflicts.

In *decentralized approaches*, the overall control task is performed by a set of supervisors (Figure 1.5), each of which controls only one component of the plant ("local control") and thus is expected

to feature low complexity.

Figure 1.5: decentralized control architecture

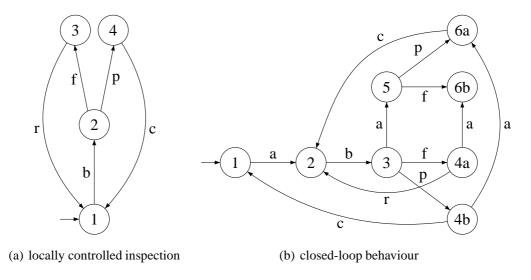

Without further measures, the plant-wide enforcement of the specification is not guaranteed, and the behaviour of the local supervisors within each other or with other plant components may be conflicting. We reconsider the manufacturing line example to illustrate such conflict situation.

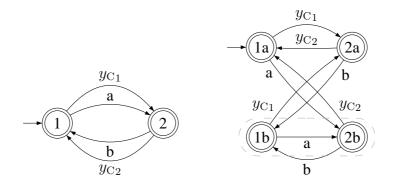

#### Example 1.2

We apply the specification for the manufacturing line (Figure 1.3 a)) separately to the machine and to the inspection unit. The resulting supervisor for the machine does not restrict its behaviour and may be omitted. The locally controlled behaviour of the inspection unit is shown in Figure 1.6 a).

Figure 1.6: Manufacturing line: decentralized control

As can be seen, the locally controlled inspection unit is free of deadlocks. When composed with the machine, the resulting behaviour of the overall plant (Figure 1.6 b)) meets the specification but, however, is blocking - observe the deadlock in state 6b.

Approaches like [CDFV88, LW90, BGK+90] guarantee safety and liveness by requiring structural conditions (see also [LW91]). However, computations still require the detailed monolithic plant model. In extended decentralized approaches ([WH91, LW97, LW02, KvS04]), the composition of the plant components and hence the exponential growth of complexity is effectively avoided. Additionally, [SMG06] provides a method to exhibit modular or decentralized supervisor design on reduced system models.

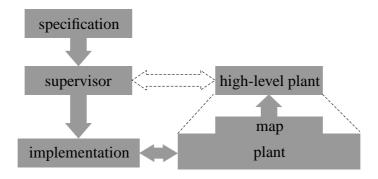

The idea of information hiding has lead to *hierarchical approaches* (e.g. based on [ZW90, WW96, dCCK02, HC02]), that map the original plant to one or more superposed layers of less complex high-level-models, where the degree of abstraction is oriented towards the according specification. The complexity is reduced by designing the supervisor for the high-level model. From this supervisor, that virtually controls the abstracted model, an implementation for the original plant has to be derived, see Figure 1.7.

Figure 1.7: hierarchical control architecture

The monotonicity of the involved operators guarantees enforcement of the specification on the original plant by the implementation. If, moreover, the abstraction of the closed loop of implementation and original plant exactly matches the closed loop of abstracted plant and supervisor, the desirable property of *hierarchical consistency* is met. If not, then the implementation can be conservative. Furthermore, measures have to be taken such that the resulting closed-loop behaviour is nonblocking. In [Led02], low- and high-level are connected by a layer of particular interfaces, and desired properties like nonblocking are achieved by a request and answer structure of the involved components. As this structure can be met individually by the plant components, the detailed monolithic plant model never needs to be computed. As one of the first approaches, applicability has been proven by physical, industry-oriented examples, see [Led96, Wen06].

By combining the hierarchical and the decentralized method, the *hierarchical-decentralized* approach ([Sch05, SMP08]) allows for a multi-level hierarchy of supervisory control by alternation of decentralized control, hierarchical abstraction and subsystem composition. The implementation of each high-level supervisor restricts the behaviour of the subordinate supervisors, down to the layer of plant components, in a way such that the whole architecture is hierarchically consistent.

Moreover, reasonable structural conditions and reasonable conditions for the abstraction map are identified that guarantee nonblocking closed-loop behaviour. The applicability of the approach to large-scale DES has been demonstrated with a laboratory case study, see also [Per04]. Extensions cover the maximal permissiveness ([SB08]) and the distributed implementation of the supervisors over communication networks ([SSZ07]).

A method that has been extensively studied in supervisory control of hybrid systems is *abstraction based control*; see e.g. [CKN98, RO98, KASL00, MR99]. In such approaches, the original plant is replaced by an approximation that relates to the original by a simple subset relation: in the abstraction, a less detailed likewise less complex description of the system behaviour allows for more possible system trajectories compared to the original plant model, see Figure 1.8.

Figure 1.8: abstraction-based control

The supervisor is designed for the abstracted model and then applied to the original plant. Similar to the hierarchical approach, safety is guaranteed by monotonicity, while liveness has to be dealt with separately.

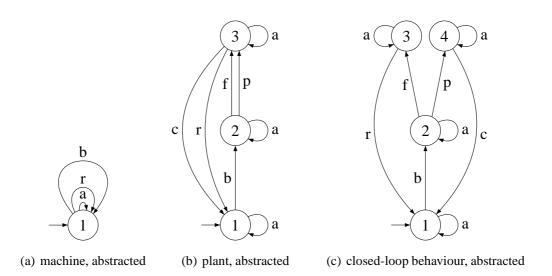

#### Example 1.3

We replace the original plant model of the manufacturing line by an abstraction to show how computational savings can be made. For the machine that can hold not more than one workpiece, we introduce a half as complex model that ignores the limited capacity, see Figure 1.9 a). Observe that any sequence of events in the original model (Figure 1.2 a)) is also possible in the abstraction, i.e. the abstraction meets the required subset relation. Also the composition with the inspection unit to an abstracted model of the plant (Figure 1.9 b)) is of lower complexity and a valid abstraction due to monotonicity of the composition operator. The realization of the abstraction-based supervisor is depicted in Figure 1.9 c).

Figure 1.9: Manufacturing line: abstraction-based control

Observe that also the supervisor realization is less complex. Unfortunately, the closed loop of the abstraction-based supervisor and the original plant matches with the blocking behaviour in Figure 1.6 b) that has also been achieved by decentralized control. Hence, as noticed before, the enforcement of the specification is preserved, while liveness, in general, is not.

Usually, the liveness of the resulting closed loop is ensured by structural conditions on the original plant and the supervisor only, such that the subset relation remains the only condition required for the abstraction. Hence, its degree can be chosen freely between arbitrary and original behaviour which can result in considerable computational savings. Naturally, too coarse abstractions lead to excessively restricted closed-loop behaviour.

#### Contribution and Outline of the Thesis

For discrete event controller design, the preservation of both, controllability and liveness properties are problems of primary concern in all approaches based on the SCT. Interestingly, these problems seem to be a specialty of the class of discrete event systems. Example: in the control of systems with continuous dynamics described according to linear systems theory, the violation of comparable properties is not observed: in the closed loop of any controller and any plant, the controller never directly changes measurement signals issued the plant, but does influence the plant output only indirectly via the plant input ( $\cong$  controllability). Also, the trajectories in the closed loop never break up, as any system accepts arbitrary input signals and always, there exists an according output signal ( $\cong$  no deadlocks). Hence, basic properties are given a priori by the input-/output-based system description rather than by additional measures in controller design.

This difference between the two fields of control theory does not lie solely in the different nature of the considered dynamics, but also in the different view on it:

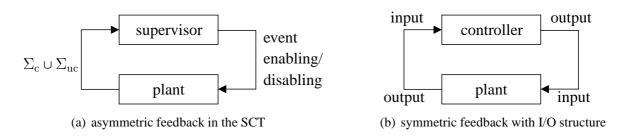

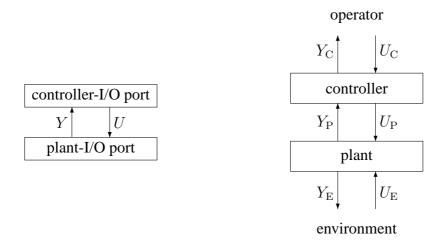

In the SCT, the plant model is interpreted as a system that by itself spontaneously generates controllable events  $\Sigma_{\rm c}$  and uncontrollable events  $\Sigma_{\rm uc}$ . The influence by a supervisor is passive, by enabling or disabling the the occurrence of controllable events. An input-/output based system description differs from this paradigm in that systems perform interaction by actively generating output signals and passively accepting output signals, see Figure 1.10 b). In [BHP+93, Wen06], the former and the latter model interpretations are denoted *asymmetric* and *symmetric* feedback, respectively.

**Figure 1.10:** Comparison of SCT- and I/O-feedback types [BHP<sup>+</sup>93]

Our approach develops an input-/output-based (I/O-based) description for DES aiming at a notion of inputs and outputs for DES that

- (i) legitimates a direction of cause and effect as in Figure 1.10 b).

- (ii) achieves controllability and basic liveness properties for the closed loop of *any* controller and *any* plant as a consequence of the I/O structure.

- (iii) allows for abstraction-based controller synthesis.

- (iv) enables hierarchical design of the plant model and the control system.

- (v) exploits the structure of composed systems similarly to decentralized approaches.

- (vi) facilitates the description of a discrete event model in separation from its surroundings via its input and output such that the model is reusable within various configurations.

In references such as [LT89, BHP $^+$ 93, Bal94, KGM95, JMRT08], discrete event models are provided with different notions of inputs and outputs, each adequate to the considered problem. In our approach and in contrast to the references, the notion of inputs and outputs and relevant fundamental properties like the novel event-based notion of  $Y_P$ -liveness are derived from J.C. Willems' behavioural systems theory [Wil91], which, due to its generality, can in principle be directly adopted

to DES to meet the above items (i) and (ii). This allows us to build on the core ideas of [MR99] on abstraction-based control of hybrid systems and the hierarchical extension [MRD03] (for items (iii) and (iv)), as both are stated within the behavioural systems theory. To meet items (iv) and (v), we introduce further extensions required for subsystem composition and a two-sided controller- and environment hierarchy. Here, we refer to approaches like [GM05, Led02, Ma04, Sch05] where the vertical (de)-composition introduced by a hierarchical architecture is complemented by a horizontal (de)-composition of modular or decentralized supervision.

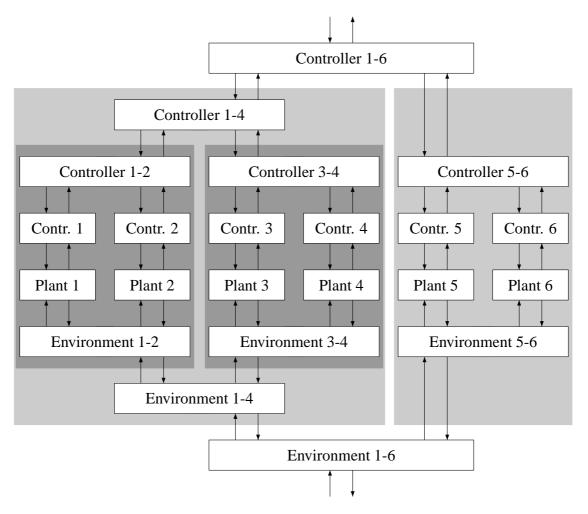

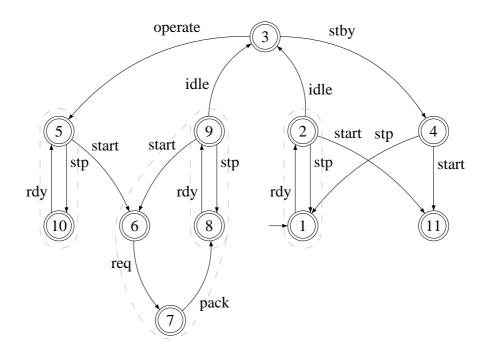

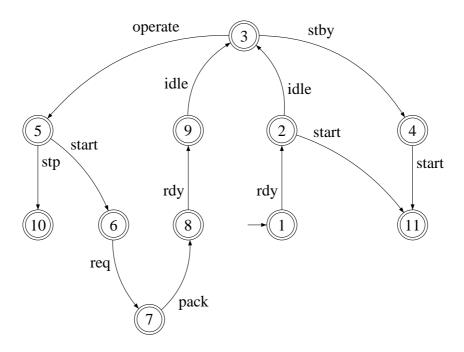

In this contribution, we propose to alternate subsystem composition and controller synthesis resulting in a hierarchical control system that complements a hierarchical plant model; see Figure 1.11.

Figure 1.11: Hierarchical control system for a plant with 6 interactive components

On the innermost level of the hierarchy, all subsystems are modeled independently from their environment aiming at reusability within various configurations. For each subsystem model, local

controllers are designed to enforce local specifications that model the desired external behaviour of the closed loop. In the design step, additional assumptions on the external configuration can be taken into account by well-defined constraints. Their enforcement is passed on to the next level of superposed control.

On the next level of the hierarchy, we use the specifications of the preceding level as an abstraction of the controlled subsystems. The admissibility of this abstraction follows directly from the I/O-based system structure. We then synthesize controllers for groups of abstracted low-level control systems. The latter have been designed independently, so constraints in interconnection of groups of subsystems (e.g. shared resources) have not yet been considered. Our framework accounts for such constraints by a hierarchy of environment models that complements the hierarchy of controllers: each dynamic environment model describes the interaction within one group of locally controlled subsystems.

The complexity of the compound group models is effectively reduced by the preceding abstraction step. As a benefit of our framework, the controllability and liveness of each hierarchical layer directly result from the I/O-based system structure. Superposed controllers designed for each group based on the abstractions solve the control problem provably also for the original groups of subsystems.

The alternation of system composition, controller synthesis, abstraction and environment interconnection is continued in a bottom-up fashion until a single top-level controller is synthesized to control an abstract overall model.

The outline of the thesis is as follows. In the following chapter, we introduce the notation and terminology of the formal language framework which is used in this thesis to elaborate and to express theoretical results. The notion of an automaton is introduced to serve as graphical representation of languages.

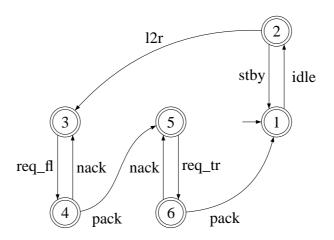

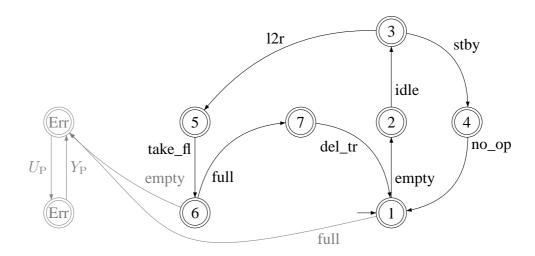

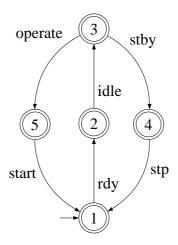

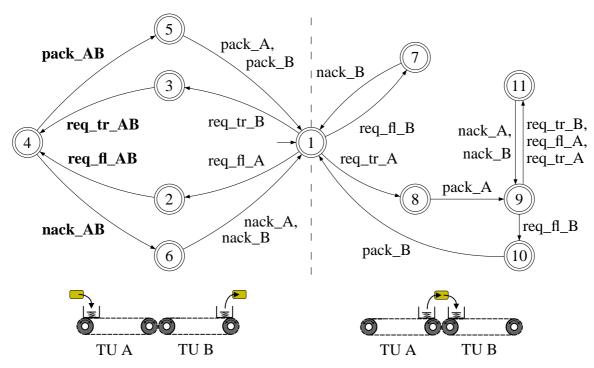

Chapter 3 proposes and explains the I/O-based description of DES and presents the definition of the I/O plant that interacts with an operator and an environment. The desired liveness properties are presented in an I/O-based formulation and in the presence of constraints on the plant's external configuration. The conceptional example of a transport unit is introduced that goes along with the whole thesis to illustrate the formal statements.

Then, the notion of an I/O controller is defined as an operator of the plant. As the first main result, an admissibility condition for the I/O controller is identified that guarantees liveness for the closed loop. Moreover, the external view on the closed loop features I/O plant properties and thus is ready for further superposed control.

Next, the controller synthesis problem is formally defined introducing the specification as a model of the external view on the desired closed loop behaviour. Finally, an important theorem is proposed stating that the original synthesis problem is readily solved based on an abstraction of the I/O plant.

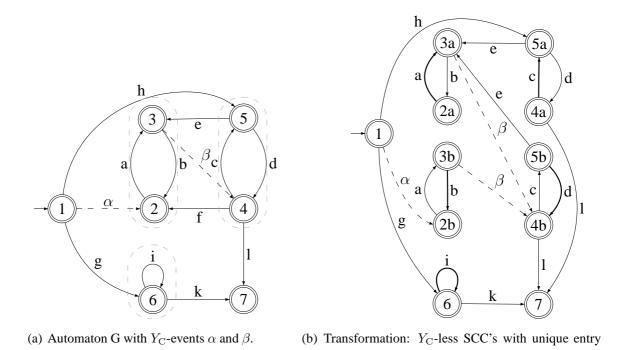

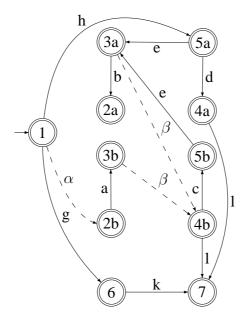

In Chapter 4, the synthesis of an admissible I/O controller is considered. The notion of  $Y_{\rm C}$ -acyclic sublanguages is introduced featuring a unique supremal element to achieve the desired  $Y_{\rm C}$ -liveness

property for the closed loop. As the controller has to meet the I/O-structure and cannot directly observe the plant's interaction with the environment, controller synthesis involves the computation of a complete, controllable and normal sublanguage. A controller synthesis procedure is presented and proven to deliver a solution to the synthesis problem, i.e. an admissible I/O controller.

Chapter 5 studies the design of a hierarchical control system as in Figure 1.11. The first part considers the description of a group of subsystems in a compound model that is ready for controller design. First a technical shuffle compound of the components is computed by the I/O shuffle operator. Then, the I/O environment model is formally defined that captures the concurrent behaviour of the components and their interaction with the remaining environment. As the main results of this chapter, I/O plant properties are proven for the external view on the compound of I/O shuffle and I/O environment. Moreover, constraints for the external configuration of the compound are identified that preserve the liveness of the involved subsystems, such that an admissible controller can be computed according to the previous chapters.

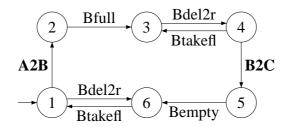

The second part of the chapter gives guidance to step by step develop a hierarchical control system based on the presented results. The applicability to multi-component DES is shown by the application to a chain of transport units and by evaluation of the complexity that results for this example.

## **Chapter 2**

# Formal Languages: Notation and Terminology

The concept of formal languages originates from computer sciences and has been adopted to a control theoretic context by the Supervisory Control Theory in order to mathematically describe the dynamical behaviour and the properties of discrete-event systems. Also in this framework, formal languages are used as the standard tool to express and prove formal statements, while finite automata serve as a graphical representation of languages. In the following, we provide an overview on the notation used in this text to describe discrete event systems in a language-based framework. For an elaborate introduction to discrete event systems, we refer to [Won08, CL08].

Alphabet, Kleene-closure and strings. Let  $\Sigma$  be a finite set of distinct symbols, called finite alphabet. The Kleene-closure  $\Sigma^*$  is the set of finite strings over  $\Sigma$ ; i.e.

$$\Sigma^* = \{s \big| \exists \, n \in \mathbb{N}, \, \forall \, \, i \leq n : \sigma_i \in \Sigma, \, s = \sigma_1 \sigma_2 \cdots \sigma_n \} \cup \{\epsilon\}$$

with the *empty string*  $\epsilon \in \Sigma^*$ . The *length* of a string  $s = \sigma_1 \cdots \sigma_n$  is denoted |s| = n, with |s| = 0 if  $s = \epsilon$  and |s| = k if  $s = \sigma_1 \cdots \sigma_k$  with  $\sigma_i \in \Sigma$  for i = 1..k. A string r = st with  $s, t \in \Sigma^*$  is called concatenation of s and t. If for two strings  $s, r \in \Sigma^*$  there exists  $t \in \Sigma^*$  such that s = rt, we say r is a *prefix* of s and write  $r \leq s$ ; moreover, r is called *strict* prefix of s if  $s \neq r$  and write r < s. A prefix of s of length  $n \in \mathbb{N}_0$  is denoted  $s^n$ .

*Language*. A language over  $\Sigma$  is a subset  $\mathcal{L} \subseteq \Sigma^*$ . Note that  $\Sigma$  itself and any of its subsets are languages. A language potentially can contain an infinite number of strings.

Operations on languages. Besides the ordinary set operations union, intersection, set difference and complement w.r.t.  $\Sigma^*$ , the following language operations are common practice, see e.g. [CL08]:

• Concatenation of  $\mathcal{L}_1, \mathcal{L}_2 \subseteq \Sigma^*$ :  $\mathcal{L}_1\mathcal{L}_2 := \{ st \in \Sigma^* | s \in \mathcal{L}_1 \land t \in \mathcal{L}_2 \}$

• Kleene-closure of  $\mathcal{L} \subseteq \Sigma^*$ :  $\mathcal{L}^* \coloneqq \{\epsilon\} \cup \mathcal{L} \cup \mathcal{LL} \cup \mathcal{LLL} \cup \cdots$

• Prefix closure of  $\mathcal{L} \subseteq \Sigma^*$ :  $\overline{\mathcal{L}} = \{r | \exists s \in \mathcal{L} : r \leq s\} \subseteq \Sigma^*$

A language  $\mathcal{L}$  is *prefix closed* if  $\mathcal{L} = \overline{\mathcal{L}}$ . The prefix closure distributes over unions, i.e.

$$\overline{\mathcal{L}_1 \cup \mathcal{L}_2} = \overline{\mathcal{L}_1} \cup \overline{\mathcal{L}_2}$$

Completeness. [KGM92]<sup>1</sup> The language  $\mathcal{L}$  is complete if

$$(\forall s \in \mathcal{L}: \exists \sigma \in \Sigma) \left[ s\sigma \in \overline{\mathcal{L}} \right]$$

(2.1)

Technically,  $\mathcal{L} = \{\emptyset\}$  is complete. A language  $\mathcal{L}$  is complete if and only if  $\overline{\mathcal{L}}$  is complete ([KGM92]).

Regular expressions and regular language. A way to represent languages over an alphabet  $\Sigma$  in a compact fashion is to use regular expressions, defined recursively as follows ([CL08]):

- 1. The empty language  $\{\emptyset\}$  is denoted by the regular expression  $\emptyset$ , the empty string language  $\{\epsilon\}$  is denoted by the regular expression  $\epsilon$ , and  $\sigma$  is a regular expression denoting the set  $\{\sigma\}$ , for all  $\sigma \in \Sigma$ .

- 2. If r and s are regular expressions, then so are rs, (r+s),  $r^*$ ,  $s^*$ , representing the concatenation, union and Kleene-closure of the sets represented by r and s, respectively.

- 3. An expression is not regular unless it is built by the finite-wise application of the above rules 1 and 2.

A language that can be represented by a regular expression is called *regular language*.

*Automaton.* Automata serve as a compact graph-based representation of languages that is useful for visualization, storage and algorithmic processing. In this text, we consider only deterministic finite automata.

#### **Definition 2.1 (Automaton [HU79])**

A deterministic finite automaton is a 5-Tuple  $G := (Q, \Sigma, \delta, q_0, Q_m)$  consisting of

- Q: the finite set of states

- $\Sigma$ : the finite alphabet

- $\delta: Q \times \Sigma \to Q$  the unique partial transition function

<sup>&</sup>lt;sup>1</sup>This notion should not be confused with the notion of complete behaviours in [Wil91].

- $q_0$ : the initial state

- $Q_m \subseteq Q$ : the set of marked states

Chapter 1 provides several examples of automata graphs. We write  $\delta(q, \sigma)!$  if  $\delta$  is defined at  $q \in Q$  and  $\sigma \in \Sigma$ . We can extend  $\delta$  to a partial function on  $Q \times \Sigma^*$  by defining recursively:

- 1.  $\delta(q, \epsilon) := q, \ \forall q \in Q$

- 2.  $\delta(q, s\sigma) = \delta(\delta(q, s), \sigma)$  whenever both  $\delta(q, s) = q' \in Q$  and  $\delta(q', \sigma)!$ .

The active event set of a state  $q \in Q$  is defined as  $\Lambda(q) := \{\sigma | \delta(q, \sigma)!\}$ . A state q with  $\Lambda(q) = \emptyset$  is called deadlock. Moreover, a state is called reachable or accessible if there exists a path from the initial state to this state. An automaton is reachable/accessible if all states are reachable/accessible. An automaton is nonblocking if from every reachable state there exists a path to a marked state. A nonblocking and reachable automaton is denoted trim. An automaton generates a prefix-closed language  $\mathcal{L}(G)$  and marks<sup>2</sup> a language  $\mathcal{L}_m(G) \subseteq \mathcal{L}(G)$  as described in the subsequent definition.

#### Definition 2.2 (Generated and Marked Language, e.g. [CL08, Won08])

For an automaton  $G = (Q, \Sigma, \delta, q_0, Q_m)$  the generated language is defined as

$$\mathcal{L}(G) \coloneqq \{ s \in \Sigma^* \mid \delta(q_0, s)! \}$$

and the marked language is

$$\mathcal{L}_{m}(G) := \{ s \in \Sigma^* \mid \delta(q_0, s) \in Q_m \}.$$

Hence, an automaton is nonblocking iff  $\mathcal{L}(G) = \overline{\mathcal{L}_m(G)}$ .

Minimal automaton and Nerode Equivalence. A deterministic automaton defines a partition of  $\mathcal{L}(G)$  and  $\mathcal{L}_m(G)$  into classes of strings leading to the same state. According to [HU79], for each regular language  $\mathcal{L}$ , there exists a (substantially) unique deterministic finite automaton, called minimal automaton, that marks  $\mathcal{L}$  with a minimal number of states.<sup>3</sup> A minimal automaton G provides a partition of  $\Sigma^*$  into strings leading to the same state that equals the partition of  $\Sigma^*$  into strings that are nerode-equivalent w.r.t.  $\mathcal{L}_m(G)$ :

<sup>&</sup>lt;sup>2</sup>In the DES literature, also the terms "accepts" and "recognizes" are used adequately to the context.

<sup>&</sup>lt;sup>3</sup>"substantially" means that the minimal automaton is unique except for isomorphisms like renaming of states.

#### Definition 2.3 (Nerode Equivalence, e.g. [Won08], orig. [Ner58])

The Nerode equivalence relation on  $\Sigma^*$  with respect to  $\mathcal{L} \subseteq \Sigma^*$  is defined as follows. For  $s, t \in \Sigma^*$ ,

$$s \equiv_{\mathcal{L}} t \iff (\forall u \in \Sigma^* : su \in \mathcal{L} \iff tu \in \mathcal{L}). \tag{2.2}$$

For  $\mathcal{L} \subseteq \Sigma^*$ , two strings  $s, t \in \Sigma^*$  with  $s \equiv_{\mathcal{L}} t$  are called *nerode-equivalent w.r.t.*  $\mathcal{L}$ . Note that all strings from the set  $\Sigma^* - \overline{\mathcal{L}}$  are nerode-equivalent w.r.t.  $\mathcal{L}$ , as they have no extension to a string of  $\mathcal{L}$ . In the minimal automaton, these strings are represented by a single state state, usually denoted "dump-state", from which there exists no path to a marked state. The dump-state usually is omitted, as only the strings belonging to  $\overline{\mathcal{L}}$  are of interest.

*Natural projection and inverse projection.* The natural projection allows to erase those events from strings whose observation is either impossible or undesirable.

#### Definition 2.4 (Natural Projection, e.g. [CL08, Won08])

The natural projection  $p_o: \Sigma^* \to \Sigma_o^*, \Sigma_o \subseteq \Sigma$ , is defined iteratively:

- 1. let  $p_o(\epsilon) := \epsilon$ ;

- 2. for  $s \in \Sigma^*$ ,  $\sigma \in \Sigma$ , let  $p_0(s\sigma) := p_0(s)\sigma$  if  $\sigma \in \Sigma_0$ , or  $p_0(s\sigma) := p_0(s)$  otherwise.

The set valued inverse of  $p_o$  is denoted  $p_o^{-1}: \Sigma_o^* \to 2^{\Sigma^*}$  and defined

$$p_0^{-1}(s) := \{t \in \Sigma^* | p_0(t) = s\} \text{ for } s \in \Sigma_0^*$$

As the above definition indicates, the projection distributes over concatenation, i.e.

$$p_{0}(st) = p_{0}(s)p_{0}(t), \ s,t \in \Sigma^{*}.$$

The projection and its inverse are defined for languages by

$$p_{o}(\mathcal{L}) \coloneqq \{p_{o}(s)|s \in \mathcal{L}\}$$

and

$$p_o^{-1}(\mathcal{L}_o) \coloneqq \{s | p_o(s) \in \mathcal{L}_o\}$$

for  $\mathcal{L} \subseteq \Sigma^*$  and  $\mathcal{L}_o \subseteq \Sigma_o^*$ , respectively.

When extended to languages, the projection distributes over unions but, in general, not over intersection, i.e.

$$p_{o}(\mathcal{L}_{1} \cup \mathcal{L}_{2}) = p_{o}(\mathcal{L}_{1}) \cup p_{o}(\mathcal{L}_{2}),$$

$$p_{o}(\mathcal{L}_{1} \cap \mathcal{L}_{2}) \subseteq p_{o}(\mathcal{L}_{1}) \cap p_{o}(\mathcal{L}_{2}) \text{ (Appendix, Lemma A.2)}$$

for  $\mathcal{L}_i \subseteq \Sigma^*$ ,  $\Sigma_o \subseteq \Sigma$ , and  $p_o$  as defined above. The inverse projection distributes over unions and intersection, i.e.

$$p_o^{-1}(\mathcal{L}_1 \cup \mathcal{L}_2) = p_o^{-1}(\mathcal{L}_1) \cup p_o^{-1}(\mathcal{L}_2),$$

$$p_o^{-1}(\mathcal{L}_1 \cap \mathcal{L}_2) = p_o^{-1}(\mathcal{L}_1) \cap p_o^{-1}(\mathcal{L}_2).$$

Prefix closure commutes with projection and inverse projection:

$$p_{o}(\overline{\mathcal{L}}) = \overline{p_{o}(\mathcal{L})},$$

$p_{o}^{-1}(\overline{\mathcal{L}}) = \overline{p_{o}^{-1}(\mathcal{L})}$

for  $\mathcal{L} \subseteq \Sigma^*$ ,  $\Sigma_o \subseteq \Sigma$ , and  $p_o$  as defined above.

*Synchronous composition.* An important operation on languages and automata is the synchronous composition, which is used to describe the interconnection of two DES.

#### Definition 2.5 (Synchronous Composition, e.g. [CL08, Won08])

The synchronous composition<sup>4</sup> of two languages  $\mathcal{L}_i \subseteq \Sigma_i^*$ ,  $i \in \{1, 2\}$ , is defined

$$\mathcal{L}_1 \parallel \mathcal{L}_2 \coloneqq p_1^{-1}(\mathcal{L}_1) \cap p_2^{-1}(\mathcal{L}_2)$$

where the projections  $p_i$  are defined with domain  $(\Sigma_1 \cup \Sigma_2)^*$  and range  $\Sigma_i^*$ .

The synchronous product of two deterministic automata  $G_1 = (Q_1, \Sigma_1, \delta_1, q_{0,1}, Q_{m,1})$  and  $G_2 = (Q_2, \Sigma_2, \delta_2, q_{0,2}, Q_{m,2})$  is

$$G_1 || G_2 \coloneqq (Q_1 \times Q_2, \Sigma_1 \cup \Sigma_2, \delta_{1||2}, (q_{0,1}, q_{0,2}), Q_{m,1} \times Q_{m,2})$$

with

$$\delta_{1\parallel 2}((q_1,q_2),\sigma)\coloneqq \begin{cases} (\delta_1(q_1,\sigma),\delta_2(q_2,\sigma)) & \text{if} \quad \sigma\in\Lambda_1(q_1)\cap\Lambda_2(q_2)\\ (\delta_1(q_1,\sigma),q_2) & \text{if} \quad \sigma\in\Lambda_1(q_1)-\Sigma_2\\ (q_1,\delta_2(q_2,\sigma)) & \text{if} \quad \sigma\in\Lambda_2(q_2)-\Sigma_1\\ & \text{undefined} & \text{else} \end{cases}$$

<sup>&</sup>lt;sup>4</sup>Also denoted parallel composition or synchronous product

The synchronous composition of two automata represents the synchronous composition of the corresponding languages:  $\mathcal{L}(G_1 \parallel G_2) = \mathcal{L}(G_1) \parallel \mathcal{L}(G_2)$  and  $\mathcal{L}_m(G_1 \parallel G_2) = \mathcal{L}_m(G_1) \parallel \mathcal{L}_m(G_2)$ .

Sequential behaviours and  $\omega$ -languages. [KGM92, TW94b, TW94a] In order to describe and analyze the sequential (also called infinite) behaviour of DES, the notion of infinite-length, so-called  $\omega$ -strings is useful. The set of  $\omega$ -strings over  $\Sigma \subseteq \Sigma$  is denoted

$$\Sigma^{\omega} = \{ s | \forall i \in \mathbb{N}_0 : \sigma_i \in \Sigma, s = \sigma_0 \sigma_1 \sigma_2 \cdots \}.$$

If for two strings  $w \in \Sigma^{\omega}$ ,  $r \in \Sigma^{*}$ , there exists  $v \in \Sigma^{\omega}$  such that w = rv, we say r is a *strict prefix* of w and write r < w. The strict prefix of w with length  $n \in \mathbb{N}_0$  is denoted  $w^n$ . An  $\omega$ -language over  $\Sigma^{\omega}$  is a subset  $\mathcal{L} \subseteq \Sigma^{\omega}$ . The *prefix* of an  $\omega$ -language  $\mathcal{L} \subseteq \Sigma^{\omega}$  is defined

$$\operatorname{pr}(\mathcal{L}) = \{r | \exists s \in \mathcal{L} : r < s\} \subseteq \Sigma^*.$$

For convenience, for  $\operatorname{pr}(\mathcal{L})$  we adopt the notation  $\overline{\mathcal{L}}$  from the domain  $\Sigma^*$ , i.e. for  $\mathcal{L} \subseteq \Sigma^{\omega}$  we denote  $\overline{\mathcal{L}} := \operatorname{pr}(\mathcal{L})$ . For a language  $\mathcal{L} \subseteq \Sigma^*$  the *limit* is defined

$$\mathcal{L}^{\infty} = \{ w \in \Sigma^{\omega} | \exists (n_i)_{i \in \mathbb{N}_0}, n_{i+1} > n_i : w^{n_i} \in \mathcal{L} \}.^5$$

We define the  $\omega$ -languages represented by an automaton  $G := (Q, \Sigma, \delta, q_0, Q_m)$  as (cf. [KGM92])

$$\mathcal{L}^{\infty}(G) := (\mathcal{L}(G))^{\infty} = \{s | \exists (n_i)_{i \in \mathbb{N}_0}, n_{i+1} > n_i : \delta(q_0, s^{n_i})! \} \text{ and }$$

$$\mathcal{L}^{\infty}_{\mathrm{m}}(G) := (\mathcal{L}_{\mathrm{m}}(G))^{\infty} = \{s | \exists (n_i)_{i \in \mathbb{N}_0}, n_{i+1} > n_i : \delta(q_0, s^{n_i}) \in Q_m \}.$$

It is easily verified that the limit operator is monotonic:

#### Lemma 2.1

Let  $\mathcal{L}_1$ ,  $\mathcal{L}_2$  be regular languages over  $\Sigma^*$ . Then:

$$\mathcal{L}_1 \subseteq \mathcal{L}_2 \Rightarrow \mathcal{L}_1^{\infty} \subseteq \mathcal{L}_2^{\infty} \tag{2.4}$$

**Proof** Pick an arbitrary string  $w \in \mathcal{L}_1^{\infty}$ . Hence  $\exists (n_i)_{i \in \mathbb{N}_0}, n_{i+1} > n_i : w^{n_i} \in \mathcal{L}_1$ . As  $\mathcal{L}_1 \subseteq \mathcal{L}_2$ ,  $\forall n_i : w^{n_i} \in \mathcal{L}_2$  and thus  $w \in \mathcal{L}_2^{\infty}$ .

In general, the reverse direction is false: consider  $\mathcal{L}_1 = a^* \cup \{b\}$ ,  $\mathcal{L}_2 = a^* \cup c^*$ , both over the alphabet  $\Sigma = \{a, b, c\}$ , where  $\mathcal{L}_1^{\infty} \subseteq \mathcal{L}_2^{\infty}$  but  $\mathcal{L}_1 \notin \mathcal{L}_2$ .

The completeness property has a strong impact on the relation between a language and its limit. The following lemma states that a string that is prefix of a string in a complete language at the same time is a prefix of an infinite string in the limit of this language, i.e. contributes to this limit.

Observe that  $(n_i)_{i \in \mathbb{N}_0}$  denotes an *infinite* sequence defining  $n_i$  for all  $i \in \mathbb{N}_0$ .

#### Lemma 2.2

For a language  $\mathcal{L} \subseteq \Sigma^*$ , the following equivalence holds:

$$\mathcal{L}$$

is complete  $\Leftrightarrow \overline{\mathcal{L}} = \overline{\mathcal{L}^{\infty}}$

#### **Proof**

"\(\infty\)": Pick any  $s \in \mathcal{L} \subseteq \overline{\mathcal{L}}$ . Thus,  $s \in \overline{\mathcal{L}^{\infty}}$ , i.e. there exists  $w \in \Sigma^{\omega}$  such that  $sw \in \mathcal{L}^{\infty}$ . Note that w is an infinite sequence. Hence, there exists  $\sigma \in \Sigma$  such that  $s\sigma < sw$  and consequently  $s\sigma \in \overline{\mathcal{L}^{\infty}}$ . Thus,  $s\sigma \in \overline{\mathcal{L}}$ , i.e.  $\mathcal{L}$  is complete.

" $\Rightarrow$ ":  $\overline{\mathcal{L}} \supseteq \overline{\mathcal{L}^{\infty}}$  is obvious. We show  $\overline{\mathcal{L}} \subseteq \overline{\mathcal{L}^{\infty}}$ . Pick an arbitrary string  $s_1 \in \overline{\mathcal{L}}$  and proceed with the following algorithm:

- (i) i = 1

- (ii) As  $s_i \in \overline{\mathcal{L}}$  there exists  $r_i \in \Sigma^*$  such that  $s_i r_i \in \mathcal{L}$ .

- (iii) As  $\mathcal{L}$  is complete, there exists  $\sigma_i$  such that  $s_i r_i \sigma_i \in \overline{\mathcal{L}}$ .

- (iv) Save  $s_{i+1} := s_i r_i \sigma_i$ , set i = i + 1 and proceed with step (ii).

By n-wise iteration of the above algorithm, a sequence  $s_1r_1 < s_2r_2 < ... < s_nr_n$  can be constructed, where  $n \in \mathbb{N}$  is arbitrary. Thus, there exists an infinite string  $w \in \Sigma^{\omega}$  with  $w^n = s_nr_n \in \mathcal{L}$  for infinitely many  $n \in \mathbb{N}$ . Hence,  $w \in \mathcal{L}^{\infty}$ . As  $s_1 < s_1r_1 < w$ , it holds that  $s_1 \in \overline{\mathcal{L}^{\infty}}$  and thus  $\overline{\mathcal{L}} \subseteq \overline{\mathcal{L}^{\infty}}$ .

By the above lemma, the prefix-closure of a complete language equals the prefix of its limit. Hence, we receive the following statement, if the language is additionally prefix-closed.

#### Lemma 2.3 ([KGM92])

For a language  $\mathcal{L} \subseteq \Sigma^*$ , the following equivalence holds:

$$\mathcal{L}$$

is complete and prefix-closed  $\Leftrightarrow \mathcal{L} = \overline{\mathcal{L}^{\infty}}$

The natural projection for  $\omega$ -strings carries over from finite strings in a straightforward way, see Definition 2.6. The range, however, is the union of finite and  $\omega$ -strings. In contrast, the set valued inverse projection maps  $\omega$ -strings to  $\omega$ -languages.

#### **Definition 2.6**

The natural projection of infinite strings  $p_o: \Sigma^{\omega} \to \Sigma_o^* \cup \Sigma_o^{\omega}, \Sigma_o \subseteq \Sigma$ , is defined:

for

$$s = \sigma_1 \sigma_2 \sigma_3 \cdots \in \Sigma^{\omega}$$

:  $p_o(s) := p_o(\sigma_1) p_o(\sigma_2) p_o(\sigma_3) \cdots$ .

The set valued inverse  $p_{\rm o}^{-1}$ :  $\Sigma_{\rm o}^* \cup \Sigma_{\rm o}^\omega \to 2^{\Sigma^* \cup \Sigma^\omega}$  is defined

$$p_o^{-1}(s) \coloneqq \{t \in \Sigma^* \cup \Sigma^\omega | p_o(t) = s\} \text{ for } s \in \Sigma_o^* \cup \Sigma_o^\omega$$

The projection and its inverse are defined for  $\omega$ -languages by

$$p_{o}(\mathcal{L}) := \{p_{o}(s) \in \Sigma_{o}^{*} \cup \Sigma_{o}^{\omega} | s \in \mathcal{L}\}$$

and

$$p_o^{-1}(\mathcal{L}_o) \coloneqq \{ s \in \Sigma^* \cup \Sigma^\omega | p_o(s) \in \mathcal{L}_o \}$$

for  $\mathcal{L} \subseteq \Sigma^* \cup \Sigma^\omega$  and  $\mathcal{L}_o \subseteq \Sigma_o^* \cup \Sigma_o^\omega$ , respectively. Accordingly, the Definition 2.5 of the synchronous product is extended to  $\omega$ -languages. For prefix-closed languages  $\mathcal{L}_1$  and  $\mathcal{L}_2$  we have

$$\mathcal{L}_1^{\infty} \parallel \mathcal{L}_2^{\infty} \subseteq (\mathcal{L}_1 \parallel \mathcal{L}_2)^{\infty},$$

see Appendix, Lemma A.3, where equality does not hold, in general (see Appendix, Lemma A.4).

This chapter introduced the notation, terminology, representation and properties of formal languages to an amount that provides a technical basis for the input-output based description of discrete event systems in the following chapter.

## **Chapter 3**

# **Discrete Event Systems with Inputs and Outputs**

In systems theory and especially in control theory, a major interest lies in how a system is influenced by its surroundings and how, in return, the system influences its surroundings. The input-output-based (I/O-based) representation of systems as it is widely used in control theory evolved from that perception. In this chapter, an I/O-based view is introduced for discrete event systems. First, we extend the language-based description of discrete event systems (Section 3.1) by the notion of I/O ports in Section 3.2 to describe the interaction of a system with its surroundings via inputs and outputs. The I/O based representation of a plant model and its liveness properties under external influence in Sections 3.3 to 3.5 is followed by an I/O-based view of a controller (Section 3.6). The main ideas of this chapter have been published in [PMS06] and [PMS07a].

### 3.1 System Description

We use formal languages to describe the dynamical behaviour of a discrete-event process as a mathematical system model. In our framework, a *system* consists of an alphabet that carries the totality of all possible events and a language over that alphabet describing all possible event sequences.

#### **Definition 3.1 (System)**

A system is a tuple  $S = (\Sigma, \mathcal{L})$  with the alphabet  $\Sigma$  and the language  $\mathcal{L} \subseteq \Sigma^*$ .

This definition strongly corresponds to Willems' definition of a *mathematical model* of a phenomenon.<sup>1</sup> Moreover, Definition 3.1 leaves room for a separate definition of the terms input and

<sup>&</sup>lt;sup>1</sup>For discrete-event processes, the mathematical model according to Willems' definition could be chosen as  $(\Sigma^*, \mathcal{L})$ , with the universe  $\Sigma^*$ .

output.

We say the system complete if  $\mathcal{L}$  is complete, the system is regular if  $\mathcal{L}$  is regular, the system is prefix-closed if  $\mathcal{L}$  is prefix-closed etc.

#### Remark 3.1

Our notion of liveness is not expressed by marked strings, and in this thesis, we consider prefix-closed systems only. Ongoing research includes the consideration of non-prefix-closed systems  $S = (\Sigma, \mathcal{L})$  with the instantaneous behaviour  $\overline{\mathcal{L}}$  and the infinite (i.e. long-term) behaviour  $\mathcal{L}^{\infty}$  (rather than  $(\overline{\mathcal{L}})^{\infty}$ ). An according automaton representation generates  $\overline{\mathcal{L}}$  and marks  $\mathcal{L}$ . Such system, if complete, additionally features the property of "eventuality" in that it provides a persistent guarantee (rather than a chance) for strings of  $\overline{\mathcal{L}}$  to be extended to a marked string of  $\mathcal{L}$ . This extended system description (including the prefix-closed case) augments the expressiveness of the system models and allows to specify a wider range of control tasks.

We introduce inputs and outputs for discrete event systems by the notion of I/O ports, via which systems perform interaction.

#### 3.2 I/O Ports

The interaction of a plant model with its surroundings via input and output is described by the following notion of a plant-I/O port.

Figure 3.1: Plant-I/O port

#### **Definition 3.2 (Plant-I/O Port)**

A pair (U, Y) is a *plant-I/O port* of the system  $(\Sigma, \mathcal{L})$  if

(i)

$$\Sigma = W \dot{\cup} U \dot{\cup} Y$$

,  $U \neq \emptyset \neq Y$ ;

(ii)

$$\mathcal{L} \subseteq \overline{(YU+W)^*}$$

; and

(iii)

$$(\forall s \in \Sigma^* Y, \mu \in U) [s \in \mathcal{L} \Rightarrow s\mu \in \mathcal{L}].$$

By item (i), we separate input events  $\mu \in U$  from output events  $\nu \in Y$ . Note that the partition into input and output alphabet does not coincide with the controllability of events: e.g. a sensor event

may at the same time be an output of one system and an input of another system. By item (ii), we require alternation of output and input events aiming at a dependence between cause and effect. Remaining dynamics (e.g. dynamics performed on another I/O port) is captured by  $W^*$ . When the system *generates* some output event  $\nu \in Y$  on the plant-I/O port it will *accept* any input event  $\mu \in U$  as an immediate successor (item (iii)) respecting that the input can be imposed freely by the systems surroundings. Consistent with the definition, the incoming arrow in Figure 3.1 denotes that U is accepted, while the emanating arrow denotes that Y is generated.

The following definition of a controller-I/O port is complementary in the sense that it requires the system to accept any event  $\nu \in Y$  as input and to reply by some event  $\mu \in U$  as output, after an optional negotiation with some other system via the alphabet W; see Figure 3.2. A controller-I/O port can be connected with a plant-I/O port, see Proposition 3.1 below.

Figure 3.2: Controller-I/O port

#### **Definition 3.3 (Controller-I/O Port)**

A pair (U, Y) is a *controller-I/O port* of the system  $(\Sigma, \mathcal{L})$  if

- (i)  $\Sigma = W \dot{\cup} U \dot{\cup} Y$ ,  $U \neq \emptyset \neq Y$ ;

- (ii)  $\mathcal{L} \subseteq \overline{(YW^*U)^*}$ ; and

(iii)

$$(\forall s \in \Sigma^* U \cup \{\epsilon\}, \ \nu \in Y) [s \in \mathcal{L} \Rightarrow s\nu \in \mathcal{L}].$$

The above notion of a I/O ports relates to Willems' description of I/O behaviours with free input and an output that does not anticipate the input. In contrast to e.g. [Wil91], we do not require the output to process the input and thereby account for non-deterministic external behaviour.

A controller-I/O port of one system can be connected with a plant-I/O of another system port to achieve a simple feedback structure as in Figure 1.10 b) that preserves completeness:

#### **Proposition 3.1**

Let (U, Y) be a plant-I/O port of the complete system  $S_1 = (\Sigma, \mathcal{L}_1)$ , and let (U, Y) be a controller-I/O port of the complete system  $S_2 = (\Sigma, \mathcal{L}_2)$  with  $\Sigma = U \cup Y$ .

Then the feedback structure  $S_{1,2} = (\Sigma, \mathcal{L}_1 \parallel \mathcal{L}_2)$  is a complete system.

**Proof** Note that  $\mathcal{L}_1$  and  $\mathcal{L}_2$  are languages over the same alphabet  $\Sigma$ , and the composition  $\mathcal{L}_{1,2} := \mathcal{L}_1 \parallel \mathcal{L}_2$  evaluates to  $\mathcal{L}_1 \cap \mathcal{L}_2$ . Hence,  $\mathcal{S}_{1,2}$  is complete whenever  $\mathcal{L}_1 = \emptyset$  or  $\mathcal{L}_2 = \emptyset$ . Now consider

$\mathcal{L}_1 \neq \emptyset \neq \mathcal{L}_2$  and pick an arbitrary string  $s \in \mathcal{L}_{1,2}$ . Observe that  $s \in \mathcal{L}_1$ ,  $s \in \mathcal{L}_2$  and that the language format  $\overline{(YU)}^*$  is met by both,  $\mathcal{L}_1$  and  $\mathcal{L}_2$ . We distinguish the following possible cases:

- (i)  $s = \epsilon$  or  $s = s'\mu$ ,  $\mu \in U$ : as  $S_1$  is complete and due to its language structure,  $s\sigma \in \mathcal{L}_1$  for some  $\sigma \in Y$ . Also,  $s\nu \in \mathcal{L}_2 \ \forall \nu \in Y$ , as (U, Y) is a controller-I/O port of  $S_2$ . In particular,  $s\sigma \in \mathcal{L}_2$ . Hence  $s\sigma \in \mathcal{L}_{1,2}$ .

- (ii)  $s = s'\nu$ ,  $\nu \in Y$ : then, as  $\mathcal{S}_2$  is complete and due to its language structure,  $s\sigma \in \mathcal{L}_2$  for some  $\sigma \in U$ . Also,  $s\mu \in \mathcal{L}_1 \ \forall \mu \in U$ , as (U,Y) is a plant-I/O port of  $\mathcal{S}_1$ . In particular,  $s\sigma \in \mathcal{L}_1$ . Hence  $s\sigma \in \mathcal{L}_{1,2}$ .

Together, for all  $s \in \mathcal{L}_{1,2}$  it holds that there exists  $\sigma \in \Sigma$  such that  $s\sigma \in \mathcal{L}_{1,2}$ , i.e.  $\mathcal{L}_{1,2}$  is complete and thus  $\mathcal{S}_{1,2}$  is complete.

The setting of Proposition 3.1 already enables the restriction of some physical plant behaviour given as a plant I/O port using a controller I/O port that exhibits actuating events in reaction to measurement events, see Figure 3.3 a). However, a standard control loop is usually equipped with an interface to some operator (e.g. by the reference variable) and a variable describing the effect of control to the environment of the plant (e.g. the control variable that is usually a system output). Based on this consideration, we aim at a control loop that extends the simple feedback structure by an interface of the controller to the operator (index C) and an interface of the plant to the environment (index E), see Figure 3.3 b).

- (a) simple feedback structure

- (b) additional interface to operator and environment

**Figure 3.3:** from simple feedback to control loop

## 3.3 I/O Plant

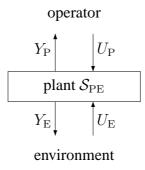

In order to achieve a high degree of modularity in our approach, we aim for a plant model description that is reusable within various configurations. To this end, we explicitly separate the plant model from its surroundings, which we identify as an operator and an environment. From the perspective of the operator, the plant models the mechanism by which the environment can be manipulated. Hence, an I/O plant is defined as a system equipped with two distinguished plant-I/O ports, see Figure 3.4  $^2$ . One port models the interaction of the plant with an operator (or controller) via events  $\Sigma_P$ , the other port models the interaction of the plant with the environment via the events  $\Sigma_P$  that are not directly observable to the operator (or controller).

Figure 3.4: I/O plant

### **Definition 3.4 (I/O Plant)**

An I/O plant is a tuple  $S_{PE} = (U_P, Y_P, U_E, Y_E, \mathcal{L}_{PE})$ , where

- (i)  $(\Sigma_{PE}, \mathcal{L}_{PE})$  is a system with  $\Sigma_{PE} := \Sigma_{P} \dot{\cup} \Sigma_{E}$ ,  $\Sigma_{P} := U_{P} \dot{\cup} Y_{P}$ ,  $\Sigma_{E} := U_{E} \dot{\cup} Y_{E}$ ; and

- (ii)  $(U_{\rm P},Y_{\rm P})$  and  $(U_{\rm E},Y_{\rm E})$  are plant-I/O ports of  $(\Sigma_{\rm PE},\mathcal{L}_{\rm PE})$ .

Note that an I/O plant always possesses the language format  $\mathcal{L}_{PE} \subseteq \overline{(Y_P U_P + Y_E U_E)^*}$ . To illustrate the above definition we introduce the following conceptional example.

<sup>&</sup>lt;sup>2</sup>In this thesis the relationship between systems, alphabets and languages is consequently indicated by matching subscripts; e.g. the system  $\mathcal{S}_{ABC}$  always refers to the language  $\mathcal{L}_{ABC}$  over the alphabet  $\Sigma_{ABC}$ . Furthermore,  $\Sigma_{ABC}$  denotes the disjoint union of  $\Sigma_A$ ,  $\Sigma_B$  and  $\Sigma_C$ , and when inputs and outputs are relevant we use e.g.  $\Sigma_A = U_A \dot{\cup} Y_A$ . Similarly, the natural projection to  $\Sigma_{AB}^*$  is denoted  $\Sigma_{AB}^*$  is denoted  $\Sigma_{AB}^*$ .

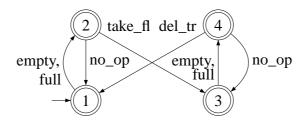

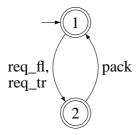

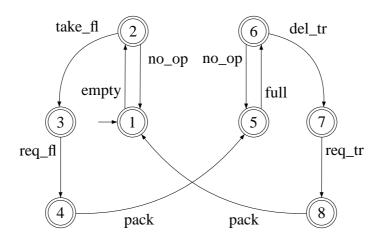

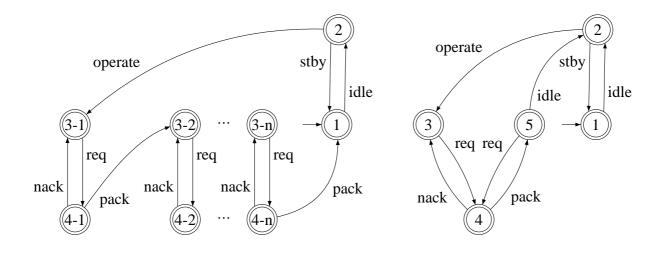

### Example 3.1

**Transport Unit.** Consider a simple transport unit (TU) as depicted in Figure 3.5 a). Its behaviour can be modeled as an I/O plant  $\mathcal{S}_{PE} := (U_P, Y_P, U_E, Y_E, \mathcal{L}_{PE})$  with  $\mathcal{L}_{PE}$  marked by the corresponding automaton model depicted in Figure 3.5 b).  $\mathcal{S}_{PE}$  is a prefix-closed system and hence, all states are marked, which is denoted by double-lined circles.

Figure 3.5: Conceptional example: Transport Unit

The TU consists of a conveyor belt carrying a box that can hold the workpiece to be transported. A spring sensor inside the box detects the absence or presence of a workpiece (empty, full). The initial state (state 1 in Fig. 3.5 b)) is defined such that the sensor reports empty. The operator can choose between three different commands (state 2). After the  $no\_op$  (no operation) command, the TU does not move, and the system remains in the initial state. The command  $del\_tr$  (deliver to right) leads to an error state as there is currently no workpiece present to deliver. Choosing the command  $take\_fl$  (take from left) prompts the TU to move the box to its left border (state 3). Now it depends on the environment if a workpiece is provided from the left, which is modeled by the event  $req\_fl$  unobservable to the operator. For a plant description that is independent from the environment, we introduce the environment-events pack and nack (positive/negative acknowledge) respecting that the environment may or may not comply with the requests of the plant. If the environment is not in the condition to provide a workpiece (nack), the request is repeated. When a workpiece is provided from the environment, the sensor reports full. Now (state 6), the command  $take\_fl$  leads to an error behaviour (the box can carry only one workpiece), and after  $no\_op$  the plant still reports full. By the command  $del\_tr$ , the belt

moves the box to the right border. The event  $req\_tr$  models the need for the workpiece to be withdrawn to the right by the environment. In case of pack, the system returns to its initial state. By  $(U_P, Y_P) := (\{no\_op, take\_fl, del\_tr\}, \{empty, full\})$ , we identify the interaction with the operator,  $(U_E, Y_E) := (\{pack, nack\}, \{req\_fl, req\_tr\})$  describes interaction with the environment. Note that  $(U_P, Y_P, U_E, Y_E, \mathcal{L}_{PE})$  features all I/O-plant properties of Definition 3.4.

Clearly, an automaton  $G = (\Sigma, Q, \delta, q_0, Q_m)$  that represents an I/O plant must itself have a certain structure such as an I/O plant has, see e.g. Figure 3.5 b). The knowledge of this structure is helpful e.g. for the graph-based design of an I/O plant model, the graph-based test for I/O plant properties or a structured graph-based visualization of an I/O plant (like the hierarchical arrangement of the states in Figure 3.5 b)). The following definition provides such an automata structure that corresponds to an I/O plant.

### **Definition 3.5 (I/O-Plant Form)**

A generator  $G := (\Sigma, Q, \delta, q_0, Q_m)$  is in *I/O-plant form* if

- (i)  $\Sigma = U_P \dot{\cup} Y_P \dot{\cup} U_E \dot{\cup} Y_E$  with nonempty alphabets  $U_P$ ,  $Y_P$ ,  $U_E$ ,  $Y_E$

- (ii)  $Q = Q_{Y} \dot{\cup} Q_{UP} \dot{\cup} Q_{UE}$

- (iii)  $q_0 \in Q_Y$

- (iv)  $[\forall q \in Q_Y, \sigma \in \Sigma](\delta(q, \sigma)! \Rightarrow (\sigma \in Y_P \land \delta(q, \sigma) \in Q_{UP}) \lor (\sigma \in Y_E \land \delta(q, \sigma) \in Q_{UE}))$

- (v)  $[\forall q \in Q_{\text{UP}}, \sigma \in \Sigma](\delta(q, \sigma)! \Rightarrow (\sigma \in U_{\text{P}} \land \delta(q, \sigma) \in Q_{\text{Y}}))$

- (vi)  $[\forall q \in Q_{\mathrm{UE}}, \sigma \in \Sigma](\delta(q, \sigma)! \Rightarrow (\sigma \in U_{\mathrm{E}} \land \delta(q, \sigma) \in Q_{\mathrm{Y}}))$

- (vii)  $[\forall q \in Q_{UP}, \mu \in U_P](\delta(q, \sigma)!)$

- (viii)  $[\forall q \in Q_{\text{UE}}, \mu \in U_{\text{E}}](\delta(q, \sigma)!)$

- (ix)  $Q_{\rm m} = Q$

- (x) G is accessible.

### Remark 3.2

Property (ix) guarantees that G represents a prefix-closed system. Properties (ix) and (x) imply that G is trim.

### Lemma 3.1

If a generator  $G := (\Sigma, Q, \delta, q_0, Q_m)$  is in I/O-plant form, then the system  $(\Sigma, \mathcal{L}_m(G))$  is an I/O plant.

**Proof** Preliminary note: Note that property (ix) implies  $q_0 \in Q_m$ . Hence,  $\mathcal{L}_m(G) \neq \emptyset$ . We now prove that  $(\Sigma, \mathcal{L}_m(G))$  provides all I/O-plant properties.

- (i)  $(\Sigma, \mathcal{L}_{\mathrm{m}}(G))$  is a system: by definition, G recognizes the language  $\mathcal{L}_{\mathrm{m}}(G)$  over  $\Sigma$ . Property (i) requires  $\Sigma = U_{\mathrm{P}}\dot{\cup}Y_{\mathrm{P}}\dot{\cup}U_{\mathrm{E}}\dot{\cup}Y_{\mathrm{E}}$ , and we identify  $\Sigma_{\mathrm{PE}} = \Sigma_{\mathrm{P}}\dot{\cup}\Sigma_{\mathrm{E}} \coloneqq \Sigma$  with  $\Sigma_{\mathrm{P}} \coloneqq U_{\mathrm{P}}\dot{\cup}Y_{\mathrm{P}}$  and  $\Sigma_{\mathrm{E}} \coloneqq U_{\mathrm{E}}\dot{\cup}Y_{\mathrm{E}}$ .

- (ii)  $(U_P, Y_P)$  and  $(U_E, Y_E)$  are plant-I/O ports of  $(\Sigma, \mathcal{L}_m(G))$ . Proof: we show that  $(U_P, Y_P)$  provides all plant-I/O port properties. The plant-I/O port property of  $(U_P, Y_P)$  carries over to  $(U_E, Y_E)$  by uniform substitution.

- (ii.i) From property (i) in Definition 3.5 we directly conclude  $\Sigma = W \dot{\cup} U_P \dot{\cup} Y_P$  (with  $W = \Sigma U_P Y_P = U_E \dot{\cup} Y_E$ ) and  $U_P \neq \emptyset \neq Y_P$ .

- (ii.ii)  $\mathcal{L}_{\mathrm{m}}(G)\subseteq\overline{(W^*(Y_{\mathrm{P}}U_{\mathrm{P}})^*)^*}$  with  $W^*=(Y_{\mathrm{E}}^*U_{\mathrm{E}}^*)^*$ . Proof: If  $\mathcal{L}_{\mathrm{m}}(G)=\{\epsilon\}$ , obviously  $\mathcal{L}_{\mathrm{m}}(G)\subseteq\overline{(W^*(Y_{\mathrm{P}}U_{\mathrm{P}})^*)^*}$ . For  $\mathcal{L}_{\mathrm{m}}(G)\supset\{\epsilon\}$ , we continue with induction: Pick arbitrary  $\sigma\in\mathcal{L}_{\mathrm{m}}(G)\cap\Sigma$ . Hence,  $\delta(q_0,\sigma)!$ . As property (iii) requires  $q_0\in Q_{\mathrm{Y}}$ , property (iv) implies  $\sigma\in Y_{\mathrm{P}}$  or  $\sigma\in Y_{\mathrm{E}}$ . Both cases prove  $\sigma\in\overline{(W^*(Y_{\mathrm{P}}U_{\mathrm{P}})^*)^*}$ . Now consider a nonempty string  $s\sigma_{n+1}=\sigma_1\sigma_2\dots\sigma_n\sigma_{n+1},\ \sigma_i\in\Sigma,\ i=1..n,\ n\in\mathbb{N}$  with  $s\sigma_{n+1}\in\mathcal{L}_{\mathrm{m}}(G)$ . Assume  $s\in\overline{(W^*(Y_{\mathrm{P}}U_{\mathrm{P}})^*)^*}$ . We show that  $s\sigma_{n+1}\in\overline{(W^*(Y_{\mathrm{P}}U_{\mathrm{P}})^*)^*}$ . Note that there exists some  $q\in Q$  such that  $\delta(q,\sigma_n)!$  and  $\delta(q,\sigma_n\sigma_{n+1})!$  and distinguish two cases:

- (a)  $\sigma_n \in Y_E \cup Y_P$ . In this case, properties (v) and (vi) rule out  $q \in Q_{UP} \cup Q_{UE}$ . Because of property (ii), we can conclude  $q \in Q_Y$ . If  $\sigma_n \in Y_E$ , property (iv) requires  $\delta(q, \sigma_n) \in Q_{UE}$ . Consequently, property (vi) implies  $\sigma_{n+1} \in U_E$ . Hence,  $s\sigma_{n+1} \in \overline{(W^*(Y_PU_P)^*)^*Y_EU_E} \subseteq \overline{(W^*(Y_PU_P)^*)^*}$ . If  $\sigma_n \in Y_P$ , property (iv) requires  $\delta(q, \sigma_n) \in Q_{UP}$ . Consequently, property (vii) implies  $\sigma_{n+1} \in U_P$ . Hence,  $s\sigma_{n+1} \in \overline{(W^*(Y_PU_P)^*)^*Y_PU_P} \subseteq \overline{(W^*(Y_PU_P)^*)^*}$ .

- (b)  $\sigma_n \in U_P \cup U_E$ . Then, property (iv) rules out  $q \in Q_Y$ . Because of property (ii), we can conclude  $q \in Q_{UP} \cup Q_{UE}$ . Hence, properties (v) and (vi) imply  $\delta(q, \sigma_n) \in Q_Y$ . Consequently,  $\sigma_{n+1} \in Y_E \cup Y_P$  follows from property (iv). Hence,  $s\sigma_{n+1} \in \overline{[(W^*(Y_PU_P)^*)^*(U_P \vee U_E) \cap \overline{(W^*(Y_PU_P)^*)^*}]}(Y_P \vee Y_E) \subseteq \overline{(W^*(Y_PU_P)^*)^*}$ .

Thus,  $s\sigma_{n+1} \in \overline{(W^*(Y_PU_P)^*)^*}$  whenever  $s \in \overline{(W^*(Y_PU_P)^*)^*}$ , which proves the induction step.

(ii.iii)  $(\forall s \in \Sigma^* Y_P, \mu \in U_P)[s \in \mathcal{L}_m(G) \Rightarrow s\mu \in \mathcal{L}_m(G)]$ . Proof: Pick arbitrary  $s\nu \in \mathcal{L}_m(G), \ \nu \in Y_P$ . Write  $q := \delta(q_0, s)$  and observe  $\delta(q, \nu)!$ . As  $\nu \notin U_P \cup U_E$ , properties (v) and (vi) rule out  $q \in Q_{UP} \cup Q_{UE}$ . Because of property (ii),  $q \in Q_Y$ . Thus, as  $\nu \in Y_P$ , property (iv) implies that  $q' := \delta(q, \nu) \in Q_{UP}$ . Consequently, property (vii) implies that for all  $\mu \in U_P$  it holds that  $\delta(q', \mu)!$ . Hence,  $s\nu\mu \in \mathcal{L}_m(G)$  for all  $\mu \in U_P$ .

Thus,  $(U_P, Y_P)$  and  $(U_E, Y_E)$  are plant-I/O ports of  $(\Sigma, \mathcal{L}_m(G))$ .

Consequently,  $(\Sigma, \mathcal{L}_{\mathrm{m}}(G))$  is an I/O plant.

With a given plant model, we now can approach the problem of controller design. In the field of discrete event systems, the usual design objectives are compliance with a desired behaviour that is expressed as a safety specification and compliance with certain liveness properties such that the desired behaviour is not only passively complied with but also exhibited actively. Safety properties can be expressed as a language inclusion, whereas the liveness properties of the plant strongly depend on its actual external configuration. For the discussion of the plant in a variety of different external configurations, we introduce the notion of constraints.

### 3.4 Constraints

Considering its definition, an I/O plant may be subject to constraints on the operator and/or the environment; e.g. the operator may or may not comply to the operator's guidelines and the environment may or may not provide resources.

### Example 3.2

**Transport Unit.** Consider the transport unit that allows for transportation of workpieces. Its ability to *continually* transport workpieces depends a) on the operator, as he has to operate the events  $del_tr$  and  $take_fl$  in a reasonable order, and b) on the environment, as it has to provide or accept workpieces from time to time.

In this framework, we describe those constraints as the variety of controller-I/O ports that can be connected to the I/O plant to obtain the desired liveness properties.

### **Definition 3.6 (Constraint)**

A *constraint* is a tuple  $(U, Y, \mathcal{L})$  if

- (i)  $(\Sigma, \mathcal{L})$  is a system with  $\Sigma = U \dot{\cup} Y$ ;

- (ii) (U,Y) is a controller-I/O port of  $(\Sigma,\mathcal{L})$ ;

- (iii)  $\mathcal{L}$  is complete.

By item (iii), we rule out constraints that preclude liveness of any I/O plant under such constraint. We refer to the *minimal constraint*  $(U, Y, \mathcal{L})$  with  $\mathcal{L} = \overline{(YU)^*}$ , if actually *no* constraint is considered, and the *maximal constraint*  $(U, Y, \mathcal{L})$  with  $\mathcal{L} = \emptyset$ . The operator and the environment constraint are denoted  $\mathcal{S}_P = (U_P, Y_P, \mathcal{L}_P)$  and  $\mathcal{S}_E = (U_E, Y_E, \mathcal{L}_E)$ , respectively.

The following definition provides an automata structure that corresponds to a constraint.

### **Definition 3.7 (Constraint Form)**

A generator  $G := (\Sigma, Q, \delta, q_0, Q_m)$  is in *constraint form* if

- (i)  $\Sigma = U \dot{\cup} Y$  with nonempty alphabets U, Y

- (ii)  $Q = Q_{Y} \dot{\cup} Q_{U}$

- (iii)  $q_0 \in Q_Y$

- (iv)  $[\forall q \in Q_Y, \sigma \in \Sigma](\delta(q, \sigma)! \Rightarrow (\sigma \in Y \land \delta(q, \sigma) \in Q_U)$

- (v)  $[\forall q \in Q_U, \sigma \in \Sigma](\delta(q, \sigma)! \Rightarrow (\sigma \in U \land \delta(q, \sigma) \in Q_Y))$

- (vi)  $[\forall q \in Q_Y, \nu \in Y](\delta(q, \sigma)!)$

- (vii)  $[\forall q \in Q](\exists \sigma \in \Sigma : \delta(q, \sigma)!)$

- (viii)  $Q_{\rm m} = Q$

- (ix) G is accessible.

### Lemma 3.2

If a generator  $G := (\Sigma, Q, \delta, q_0, Q_m)$  is in constraint form, then the system  $(\Sigma, \mathcal{L}_m(G))$  is a constraint.

**Proof** See Appendix A.2.

In our framework, the notion of liveness is consistently formulated as liveness under constraints.

### 3.5 Liveness